可编程逻辑器件 课程设计全攻略

课程设计目标

本课程设计旨在通过一个完整的数字系统设计项目,帮助你:

- 掌握硬件描述语言:熟练使用 Verilog 或 VHDL 进行数字逻辑建模与设计。

- 熟悉 EDA 工具链:学会使用 Quartus Prime (Intel/Altera)、Vivado (Xilinx) 等主流 FPGA 开发软件,完成从代码编写、功能仿真、综合、实现到最终下载的全过程。

- 理解数字系统设计方法:掌握自顶向下和自底向上的设计思想,学会模块化设计和系统级验证。

- 提升工程实践能力:锻炼解决实际问题的能力,包括调试、优化和文档撰写能力。

设计流程

一个标准的 FPGA 课程设计项目通常遵循以下流程:

-

需求分析与方案设计

- 明确功能:清晰地定义你的系统要做什么,输入是什么,输出是什么,有哪些控制信号。

- 架构设计:将复杂的系统分解为若干个功能模块(如:数据处理模块、控制状态机模块、接口模块等),并画出系统框图。

- 技术选型:选择 FPGA 开发板(如 DE10-Lite, Basys3, Nexys4 等)、HDL 语言(Verilog 或 VHDL)和开发工具。

-

模块设计与编码

- 行为/RTL级建模:使用 HDL 对每个功能模块进行代码实现,这是设计的核心,要求代码清晰、可读性强、符合规范。

- 编写 Testbench:为每个关键模块编写测试平台,用于在硬件实现前进行功能仿真,验证逻辑的正确性。

-

功能仿真

- 使用 ModelSim, QuestaSim 等仿真工具,对 Testbench 进行仿真。

- 检查仿真波形,确保所有功能符合设计预期。这是发现逻辑错误的最佳阶段。

-

综合与实现

- 综合:使用综合工具(如 Quartus Prime 的 Synthesis, Vivado 的 Synthesis)将 HDL 代码转换为由基本逻辑门(与、或、非、触发器等)构成的网表。

- 实现:包括翻译、映射、布局布 等步骤,将综合后的网表适配到所选 FPGA 的具体硬件资源上。

-

时序仿真

- 在实现后,加入 FPGA 的实际延时信息,进行更精确的仿真。

- 验证系统在最高工作频率下是否能稳定工作,检查是否存在建立/保持时间违规。

-

硬件实现与验证

- 生成编程文件:将实现后的设计生成 FPGA 可以识别的位流文件。

- 下载与调试:使用 JTAG 或 USB-Blaster 等下载器将位流文件烧录到 FPGA 芯片中。

- 板上验证:通过开发板上的按键、LED、数码管、七段显示器、串口等外设,观察实际运行结果,与预期进行对比,进行最终调试。

-

设计总结与报告撰写

整理整个设计过程,撰写课程设计报告。

设计题目推荐(由易到难)

这里提供一系列不同难度和方向的设计题目,供你选择。

A. 基础入门级

适合初学者,旨在巩固组合逻辑和时序逻辑基础。

-

数字时钟

- 功能:实现一个能显示时、分、秒的数字时钟。

- 扩展:增加闹钟功能、日期显示、按键调时功能。

- 核心模块:分频器(将外部高频时钟降为1Hz)、计数器(秒、分、时)、显示译码器(驱动数码管)。

-

交通灯控制器

- 功能:模拟十字路口的交通灯,东西、南北方向交替放行。

- 扩展:增加行人过街请求按钮,实现紧急车辆优先通行功能。

- 核心模块:状态机、计数器、LED 驱动模块。

-

密码锁

- 功能:通过 4x4 矩阵键盘输入4位密码,正确则点亮 LED,错误则报警(蜂鸣器)。

- 扩展:支持密码修改功能,输入错误次数限制。

- 核心模块:键盘扫描模块、密码比较模块、状态机控制模块。

B. 综合应用级

适合有一定基础的同学,涉及数据通路、控制器和算法实现。

-

简易计算器

- 功能:实现两个4位二进制数的加法、减法、乘法、除法。

- 扩展:支持更多位数的运算,使用七段显示器显示输入和结果。

- 核心模块:按键输入模块、运算单元、显示控制模块、顶层状态机。

-

UART 收发器

- 功能:实现一个符合 RS-232 标准的异步串口通信模块,能将 FPGA 内部数据发送到 PC,也能接收 PC 发来的数据并显示在 LED 上。

- 扩展:实现自定义的通信协议,如收发特定格式的数据包。

- 核心模块:波特率发生器、发送器(并转串)、接收器(串转并)、帧同步逻辑。

-

VGA 图像显示控制器

- 功能:在 VGA 显示器上显示一个简单的彩色图形(如彩条、棋盘格)。

- 扩展:实现一个简单的绘图板,通过鼠标或按键在屏幕上画点、画线。

- 核心模块:VGA 时序发生器、地址生成器、颜色查找表。

C. 高级挑战级

适合学有余力的同学,挑战更复杂的算法和系统。

-

简易 CPU (RISC-V / MIPS 架构)

- 功能:在 FPGA 上实现一个简化的 32 位 RISC-V 或 MIPS 指令集处理器,包括指令译码、数据通路、寄存器堆、ALU 等模块。

- 扩展:在片内实现一个简单的 SRAM 作为指令和数据存储器,编写几条汇编指令进行测试。

- 核心模块:PC、指令寄存器、数据通路、控制器(硬布线或微码)。

-

FIR/IIR 数字滤波器

- 功能:实现一个有限/无限脉冲响应数字滤波器,对输入的数字信号(如由 ADC 采集的正弦波加噪声)进行滤波处理。

- 扩展:通过串口或按键调整滤波器系数,观察滤波效果。

- 核心模块:乘法器、加法器、移位寄存器、系数存储器。

-

图像边缘检测器

- 功能:从摄像头(如 OV7670)获取图像数据,在 FPGA 上使用 Sobel 或 Prewitt 算子进行边缘检测,并将结果输出到 VGA 显示器。

- 核心模块:摄像头接口模块、图像缓存(FIFO 或 BRAM)、Sobel 运算单元、VGA 显示控制器。

报告撰写规范

一份优秀的报告是课程设计成果的重要体现,报告应包含以下部分:

- 封面:包含课程名称、题目、姓名、学号、日期、指导教师。

- 摘要:简要介绍设计目的、主要内容、采用的技术和方法、实现的功能和结论。

- 目录。

- 第一章:绪论

- 1 设计背景与意义

- 2 设计任务与目标

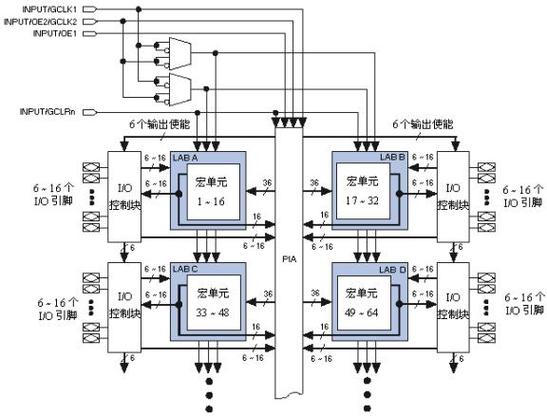

- 第二章:系统总体方案设计

- 1 设计需求分析

- 2 系统总体架构(附系统框图)

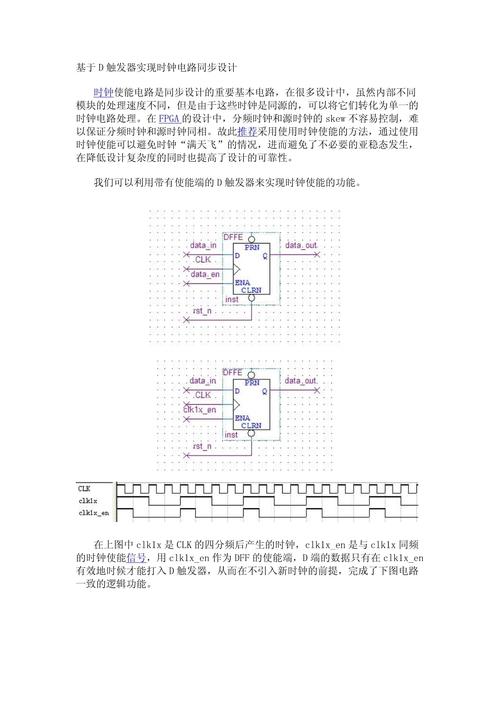

- 3 关键技术介绍

- 第三章:硬件设计与实现

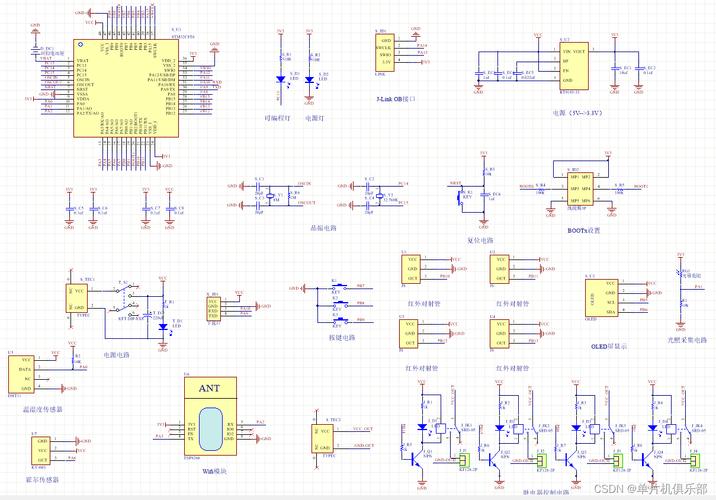

- 1 硬件平台介绍(开发板、FPGA 型号等)

- 2 核心模块设计(附每个模块的 RTL 代码和功能说明)

- 3 模块间接口定义

- 第四章:软件设计与实现

- 1 开发环境介绍(Quartus Prime/Vivado 版本)

- 2 关键算法/逻辑的 HDL 实现(附核心代码片段和注释)

- 3 Testbench 设计与仿真结果分析(附仿真波形图)

- 第五章:系统仿真与验证

- 1 功能仿真结果与分析

- 2 时序仿真结果与分析(报告时序约束和最高频率)

- 3 硬件实现与结果(附实物照片、LED/数码管/屏幕显示效果图)

- 第六章:总结与展望

- 1 设计工作总结(完成了哪些功能,达到了什么指标)

- 2 遇到的问题与解决方案

- 3 设计的不足与未来改进方向

- 参考文献

- 附录:完整的 HDL 源代码、Testbench 代码。

常用开发板推荐

- Intel/Altera 系列:

- DE10-Lite (Terasic):基于 Cyclone 10 LP FPGA,资源丰富,带 ADC、按键、LED、数码管、HDMI 输出等,性价比极高,非常适合学习和做课程设计。

- DE0-Nano (Terasic):经典入门板,基于 Cyclone IV。

- Xilinx 系列:

- Basys3 (Digilent):基于 Artix-7 FPGA,带 Arduino 接口、Pmod 扩展接口,生态系统完善,教程资源多。

- Nexys4 (Digilent):更高阶的板卡,带 HDMI 输入/输出、麦克风、SD 卡槽等,适合做更复杂的项目。

建议:在选择题目和开发板时,尽量匹配,做 VGA 项目,DE10-Lite 或 Nexys4 是很好的选择。

祝你课程设计顺利,享受从代码到硬件的奇妙旅程!

版权声明:除非特别标注,否则均为本站原创文章,转载时请以链接形式注明文章出处。